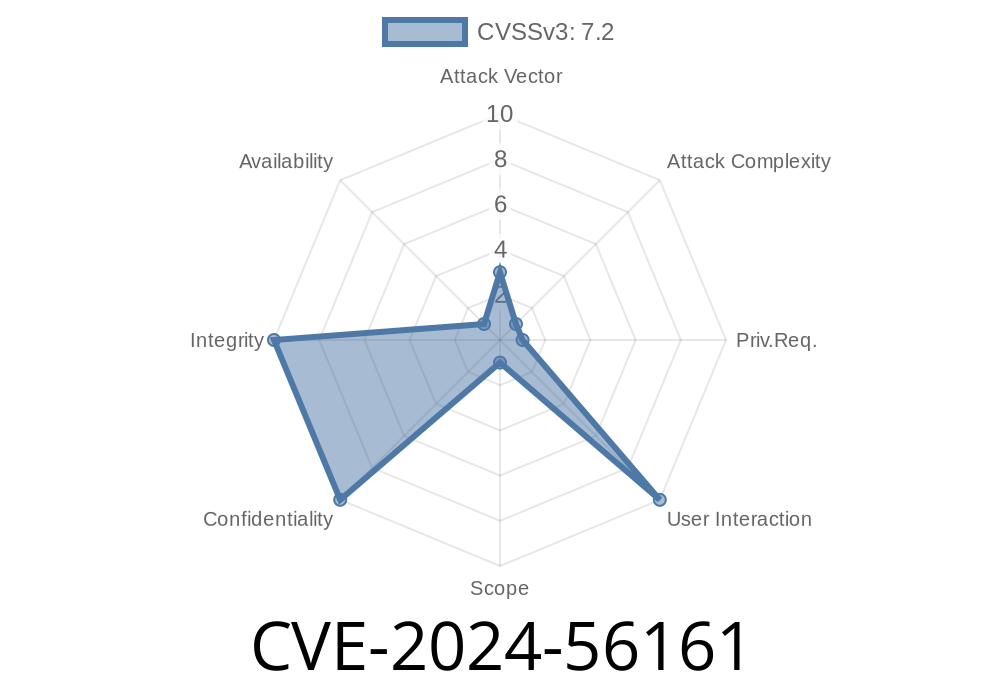

Modern CPUs are very powerful, but also very complicated, and with this complexity comes risk. This year, security researchers discovered a critical vulnerability – CVE-2024-56161 – that impacts AMD processors. Specifically, if an attacker has administrator privileges on a vulnerable system, they can load fake microcode into the CPU. This breaks the promise of virtual machine confidentiality, even under AMD's Secure Encrypted Virtualization-Secure Nested Paging (SEV-SNP) technology.

In this article, we'll break down what CVE-2024-56161 is, how it works, and why it's a real danger to cloud hosts and data centers using AMD CPUs. You'll also see code snippets and references to dig deeper.

1. What is CVE-2024-56161?

At a high level, this bug is about how the CPU loads microcode updates (these are low-level code patches for CPUs, like firmware updates). Normally, before accepting a new microcode update, the CPU needs to make sure it's genuine – that's where *signature verification* comes in.

CVE-2024-56161 happens because the signature check inside the AMD CPU ROM (Read-Only Memory) microcode patch loader isn't strict enough. This means a crafty attacker with local administrator/root access can trick the CPU into running custom, possibly malicious microcode – and the CPU will accept it as if it were official!

AMD CPUs supporting SEV-SNP virtualization security tech

- Primarily, this affects recent EPYC processors used in server/cloud environments

2. Why is This a Big Deal?

AMD's SEV-SNP (Secure Encrypted Virtualization – Secure Nested Paging) is a security feature that isolates virtual machines (VMs or "guests") from each other and even from administrators. In theory, even if you *own* the host, you shouldn't be able to read a guest VM’s secrets.

But if you can load new (malicious) microcode, that *entire foundation* is at risk! Administrators can:

Example: Microcode Patch Loader Interaction

While we can't provide actual exploit code (since this is very dangerous), here's an illustrative snippet showing how a user-mode tool would interact with the CPU to push a microcode update on Linux. Tools like microcode_ctl or fwupd use similar syscalls.

#include <stdio.h>

#include <fcntl.h>

#include <unistd.h>

#include <sys/ioctl.h>

#define MICROCODE_DEVICE "/dev/cpu/microcode"

// Microcode payload would be prepared here

unsigned char malicious_microcode[] = { /* ... crafted patch ... */ };

int main() {

int fd = open(MICROCODE_DEVICE, O_WRONLY);

if (fd < ) {

perror("open microcode device");

return 1;

}

ssize_t ret = write(fd, malicious_microcode, sizeof(malicious_microcode));

if (ret != sizeof(malicious_microcode)) {

perror("write microcode");

}

close(fd);

return ;

}

Above, if your microcode is "signed" improperly, a vulnerable CPU would load it anyway, allowing your code to run at the deepest hardware level.

4. Proof-of-Concept and Exploit Details

While a *public* weaponized exploit isn’t released (for obvious reasons), researchers confirmed exploitability by crafting custom microcode and loading it onto affected servers. In their writeups, they showed that once the microcode was loaded, previously protected secrets inside guest VMs could be extracted.

Attack Prerequisites

- Local administrator / root privileges (needed to load microcode)

Patch your system – AMD has released fixed CPU microcode. Update *immediately*.

- Minimize admin access – Only trusted staff should be allowed root/admin.

AMD Security Advisory:

AMD-SB-7014: Improper signature verification in CPU ROM

SEV-SNP Technology Whitepaper:

AMD SEV-SNP Technical Overview (PDF)

CVE Database Entry:

Linux microcode update docs:

Microcode Update in Linux (kernel docs)

7. Conclusion

CVE-2024-56161 is a powerful reminder: even with advanced CPU-level protections like SEV-SNP, a broken link like improper signature verification can bring down the whole castle. If you depend on AMD server CPUs for confidential workloads, patch as soon as humanly possible, and keep a close eye on who has admin keys to your kingdom.

Stay safe and up-to-date!

This article offers an original, simplified breakdown for IT admins, cloud operators, and security teams. Questions? Add your comment below!

Timeline

Published on: 02/03/2025 18:15:37 UTC

Last modified on: 02/04/2025 12:15:28 UTC